The applying of real-time knowledge processing or responsiveness is essential, similar to in high-performance computing, knowledge facilities, or purposes requiring low-latency knowledge transfers. It permits environment friendly use of PCIe bandwidth and assets by intelligently managing reminiscence write operations based mostly on system dynamics and workload priorities. By successfully leveraging Deferrable Reminiscence Write [DMWr], Gadgets can obtain optimized efficiency and responsiveness, aligning with the evolving calls for of contemporary computing purposes.

What Is Deferrable Reminiscence Write?

Deferrable Reminiscence Write (DMWr) ECN launched this new reminiscence transaction kind, which was later formally included in PCIe 5.0 to CXL2.0. This enhanced kind of reminiscence transaction is Deferrable Reminiscence Write [DMWr], which flows as one other kind of present Learn/Write reminiscence transaction; the key distinction of this Deferrable Reminiscence Write, the place the Requester makes an attempt to jot down to a given location in Reminiscence House utilizing the non-posted DMWr TLP Sort, it Suspending their completion of reminiscence write transactions to enhance general system effectivity and efficiency, these reminiscence write operation might be delay or deferred till different precedence job full.

The Deferrable Reminiscence Write (DMWr) requires the Completer to return an acknowledgment to the Requester and supplies a mechanism for the recipient to defer (quickly refuse to service) the Request.

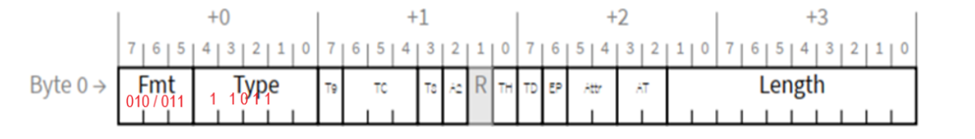

DMWr supplies a mechanism for Endpoints and hosts to decide on to hold out or defer incoming DMWr Requests. This mechanism can be utilized by Endpoints and Hosts to simplify the design of circulation management, cut back latency, and enhance throughput. The Deferrable Reminiscence writes TLP format in Determine A.

Instance State of affairs

Right here’s how the DMWr works with a simplified instance: Think about a system with an endpoint machine (System A) and a bunch CPU (System B). System B desires to jot down knowledge to System A’s reminiscence, however on account of various causes similar to system bus congestion or prioritization of different transactions, System A can defer the completion of the reminiscence write request. Simply observe these steps:

- Initiation of Reminiscence Write: System B initiates a reminiscence write transaction to System A. This entails sending the reminiscence write request together with the information payload over the PCIe bodily layer hyperlink.

- Acknowledgment and Deferral: Upon receiving the reminiscence write request, System A acknowledges the transaction however could determine to defer its completion. System A sends an acknowledgment (ACK) again to System B, indicating it has obtained the information and intends to finish the write operation however not instantly.

- Deferred Completion: System A defers the completion of the reminiscence write operation to a later, extra opportune time. This deferral permits System A to prioritize different transactions or optimize using system assets, similar to reminiscence bandwidth or processor availability.

- Completion and Response: At a later level, System A completes the deferred reminiscence write operation and sends a completion indication again to System B. This completion usually consists of any standing updates or further info associated to the transaction.

Utilization or Significance of DMWr

Deferrable Reminiscence Write utilization supplies the development within the following facets:

- Diminished Latency: By deferring much less crucial reminiscence write operations, extra crucial transactions might be processed with decrease latency, bettering general system responsiveness.

- Improved Effectivity: Optimizes the utilization of system assets similar to reminiscence bandwidth and CPU cycles, enhancing the effectivity of information transfers throughout the PCIe structure.

- Enhanced Efficiency: Permits gadgets to handle and prioritize transactions dynamically, probably rising general system throughput and decreasing competition.

Challenges within the Implementation of DMWr Transactions

The implementation of deferrable reminiscence writes (DMWr) introduces a number of developments and challenges by way of utilization and verification:

- Timing and Synchronization: DMWr permits transactions to be deferred, complicating timing necessities or finishing them inside acceptable timing home windows to keep away from protocol violations. Making certain correct synchronization between gadgets turns into crucial to forestall knowledge loss or corruption.

- Protocol Compliance: Verification should guarantee compliance with ECN PCIe 6.0 and CXL specs concerning when and the way DMWr transactions might be initiated and accomplished.

- Efficiency Optimization: Whereas DMWr can enhance general system efficiency by decreasing latency, verifying its affect on system efficiency and making certain it meets anticipated benchmarks is essential.

- Error Dealing with: Dealing with errors associated to deferred transactions provides complexity. Verifying error detection and restoration mechanisms below numerous situations (e.g., timeout throughout deferral) is crucial.

Verification Challenges of DMWr Transactions

The challenges to verifying the DMWr transaction include all checks with respect to Perform, Timing, Protocol compliance, enchancment, Error situation, and safety utilization on goal, in addition to Information integrity on the PCIe and CXL.

- Practical Verification: Verifying the right implementation of DMWr at each ends of the PCIe hyperlink (transmitter and receiver) to make sure correct performance and adherence to specs.

- Timing Verification: Validating timing constraints related to deferring writes and making certain transactions are accomplished inside specified home windows with out violating protocol guidelines.

- Protocol Compliance Verification: Checking that DMWr transactions adhere to PCIe and CXL protocol guidelines, together with ordering guidelines and any restrictions on deferral based mostly on the transaction kind.

- Efficiency Verification: Assessing the affect of DMWr on general system efficiency, together with latency discount and bandwidth utilization, by simulation and testing.

- Error State of affairs Verification: Creating and testing situations to confirm error dealing with mechanisms associated to DMWr, similar to timeouts, retries, and restoration procedures.

- Safety Concerns: Assessing potential safety vulnerabilities associated to DMWr, similar to knowledge integrity dangers throughout deferred transactions or publicity to timing-based assaults.

Main verification challenges and approaches are timing and synchronization verification within the context of implementing deferrable reminiscence writes (DMWr), which is essential because of the inherent complexities launched by deferred transactions. Listed below are the important thing points and approaches to handle them:

Timing and Synchronization Points

- Transaction Completion Timing:

- Problem: Making certain deferred transactions are accomplished throughout the specified time window with out violating protocol timing constraints.

- Strategy: Design an inner timer and checker to mannequin worst-case situations the place transactions are deferred and confirm that they’re full inside allowable latency limits. This entails simulating numerous site visitors masses and situations to evaluate timing below totally different situations.

- Ordering and Dependencies:

- Problem: Verifying that transactions deferred utilizing DMWr preserve the right ordering and dependencies relative to non-deferred transactions.

- Strategy: Implement take a look at situations that embrace combined site visitors of DMWr and non-DMWr transactions. Confirm by simulation or emulation that dependencies and ordering necessities are appropriately maintained throughout the PCIe hyperlink.

- Interrupt Dealing with and Response Occasions:

- Problem: Confirm the dealing with of interrupts and guarantee well timed responses from gadgets concerned in DMWr transactions.

- Strategy: Implement take a look at circumstances that simulate interrupt era throughout DMWr transactions. Measure and confirm the response instances to interrupts to make sure they meet system latency necessities.

In conclusion, whereas deferrable reminiscence writes in PCIe and CXL provide important efficiency advantages, their implementation and verification current a number of challenges associated to timing, protocol compliance, efficiency optimization, and error dealing with. Addressing these challenges requires rigorous testing and testbench of site visitors, superior verification methodologies, and an intensive understanding of PCIe specs and likewise the motivation behind introducing this Deferrable Write is successfully used within the CXL additional. Outcomes of Deferrable Reminiscence Write confirm that the efficiency advantages of DMWr (decreased latency, improved throughput) are achieved with out compromising timing integrity or violating protocol specs.

In abstract, PCIe and CXL are complicated protocols with many verification challenges. It’s essential to perceive many new Spec modifications and think about the sturdy verification plan for the brand new options and backward appropriate assessments impacted by new options. Cadence’s PCIe 6.0 Verification IP is totally compliant with the newest PCIe Categorical 6.0 specs and supplies an efficient and environment friendly approach to confirm the elements interfacing with the PCIe 6.0 interface. Cadence VIP for PCIe 6.0 supplies exhaustive verification of PCIe-based IP and SoCs, and we’re working with Early Adopter prospects to hurry up each verification stage.

👇Comply with extra 👇

👉 bdphone.com

👉 ultractivation.com

👉 trainingreferral.com

👉 shaplafood.com

👉 bangladeshi.assist

👉 www.forexdhaka.com

👉 uncommunication.com

👉 ultra-sim.com

👉 forexdhaka.com

👉 ultrafxfund.com

👉 bdphoneonline.com

👉 dailyadvice.us