The clock reference design stands out for its robustness and scalability, making it a really perfect answer for high-speed, multi-channel clocking wants in superior RADAR and 5G wi-fi testing environments. It provides exact synchronisation and low-phase noise, that are key to enhancing efficiency metrics like SNR and ENOB.

The arrival of superior communication applied sciences resembling RADAR and 5G has necessitated the event of extremely exact and dependable clock reference designs. These designs are vital for making certain the accuracy and stability of timing indicators in RADAR methods, which depend on exact timing for object detection and ranging, and in 5G wi-fi testers, which require impeccable synchronisation to fulfill the demanding efficiency requirements of next-generation networks. Clock reference designs are pivotal in sustaining sign integrity, minimising jitter, and enhancing total system efficiency. They’re important in purposes starting from automotive security and climate forecasting to high-speed wi-fi communications, the place even the slightest timing inaccuracies can result in important efficiency degradation.

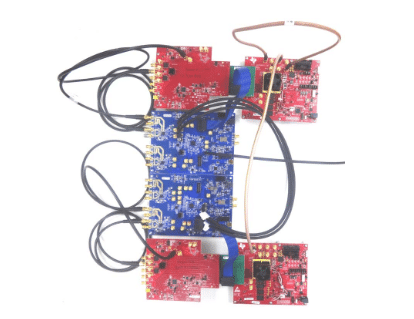

The TIDA-01024 by Texas Devices is a excessive channel depend JESD204B daisy chain clock reference design particularly tailor-made for RADAR and 5G wi-fi testers. Excessive-speed multi-channel purposes demand low noise and scalable clocking options with exact channel-to-channel skew changes to attain optimum system Sign-to-Noise Ratio (SNR), Spurious-Free Dynamic Vary (SFDR), and Efficient Variety of Bits (ENOB). This reference design facilitates the scaling of JESD204B synchronised clocks in a daisy chain configuration, offering multichannel JESD204B clocks utilizing Texas Devices (TI) LMK04828 clock jitter cleaner and LMX2594 wideband PLL with built-in VCOs, attaining a clock-to-clock skew of lower than 10 ps. This configuration has been examined with ADC12DJ3200 Analysis Modules (EVMs) at 3 GSPS, attaining a channel-to-channel skew of lower than 50 ps and improved SNR efficiency.

The design incorporates important theories guiding customers via half choice and design optimisation, offering complete documentation together with schematics, board layouts, {hardware} testing, and take a look at outcomes. The important thing options of this reference design embrace high-frequency (GSPS) pattern clock technology, excessive channel depend, and scalable JESD204 B-compliant clock answer. It additionally provides low section noise clocking for RF sampling ADC/DAC and configurable section synchronisation to attain low skew in multi-channel methods. This design helps high-speed converter and seize playing cards such because the ADC12DJ3200EVM and TSW14J56/TSW14J57.

On this scalable, multichannel phase-synchronised clock answer, every clocking board consists of two high-speed synchronised JESD204B clocks. These boards synchronise with one another utilizing a daisy-chain configuration. The primary clocking board gives reference enter indicators and sync indicators to the subsequent clocking board, persevering with this course of down the chain. Size-matched cables present these reference and sync indicators, making certain exact timing throughout the system.

The LMX2594 is a high-performance, wideband RF PLL with built-in VCO. It helps a frequency vary from 10 MHz to fifteen GHz without having an inside doubler. It operates in fractional-N and integer-N modes, that includes a 32-bit fractional divider for effective frequency choice. The high-performance PLL, with a determine of benefit of -236 dBc/Hz and a high-phase detector frequency, can obtain very low in-band noise and built-in jitter. This makes the LMX2594 appropriate for purposes in wi-fi communication testers and phased array radars.

TI has examined this reference design. It comes with a invoice of supplies (BOM), schematics, and so forth. You will discover extra knowledge in regards to the reference design on the corporate’s web site. To learn extra about this reference design, click on right here.